Programmation Flash MICROCHIP PIC24

Informations sur le produit

Programmation Flash

Les familles dsPIC33/PIC24 d'appareils disposent d'une mémoire de programme Flash interne programmable pour l'exécution du code utilisateur. Il existe jusqu'à trois méthodes pour programmer cette mémoire :

- Opération d'instruction de tableau

- Programmation série en circuit (ICSP)

- Programmation intégrée à l'application (IAP)

Les instructions du tableau fournissent la méthode de transfert de données entre l'espace mémoire du programme Flash et l'espace mémoire des données des dispositifs dsPIC33/PIC24. L'instruction TBLRDL est utilisée pour lire à partir des bits [15:0] de l'espace mémoire du programme. L'instruction TBLWTL est utilisée pour écrire dans les bits [15:0] de l'espace mémoire du programme Flash. TBLRDL et TBLWTL peuvent accéder à la mémoire programme Flash en mode mot ou en mode octet.

En plus de l'adresse de la mémoire du programme Flash, l'instruction de table spécifie également un registre W (ou un pointeur de registre W vers un emplacement mémoire), qui est la source des données de la mémoire du programme Flash à écrire, ou la destination d'un programme Flash. mémoire lue.

Cette section décrit la technique de programmation de la mémoire programme Flash. Les familles de dispositifs dsPIC33/PIC24 disposent d'une mémoire de programme Flash interne programmable pour l'exécution du code utilisateur. Il existe jusqu'à trois méthodes pour programmer cette mémoire :

- Auto-programmation d'exécution (RTSP)

- Programmation série en circuit™ (ICSP™)

- Programmation série en circuit améliorée (EICSP)

RTSP est exécuté par le logiciel d'application pendant l'exécution, tandis que ICSP et EICSP sont exécutés à partir d'un programmeur externe à l'aide d'une connexion de données série à l'appareil. ICSP et EICSP permettent un temps de programmation beaucoup plus rapide que RTSP. Les techniques RTSP sont décrites dans la section 4.0 « Auto-programmation d'exécution (RTSP) ». Les protocoles ICSP et EICSP sont définis dans les documents de spécification de programmation pour les appareils respectifs, qui peuvent être téléchargés à partir du Microchip website (http://www.microchip.com). Lors de la programmation en langage C, plusieurs fonctions intégrées sont disponibles pour faciliter la programmation Flash. Reportez-vous au « Guide de l'utilisateur du compilateur C MPLAB® XC16 » (DS50002071) pour plus de détails sur les fonctions intégrées.

Instructions d'utilisation du produit

Pour programmer la mémoire programme Flash, procédez comme suit :

- Reportez-vous à la fiche technique de l'appareil pour vérifier si la section du manuel de référence de la famille prend en charge l'appareil que vous utilisez.

- Téléchargez la fiche technique de l'appareil et les sections du manuel de référence de la famille sur Microchip Worldwide Website à: http://www.microchip.com.

- Choisissez l'une des trois méthodes pour programmer la mémoire (opération d'instruction de table, programmation série en circuit (ICSP), programmation en application (IAP)).

- Si vous utilisez l'opération d'instruction de table, utilisez l'instruction TBLRDL pour lire à partir des bits [15:0] de l'espace mémoire du programme et l'instruction TBLWTL pour écrire dans les bits [15:0] de l'espace mémoire du programme Flash.

- Assurez-vous de spécifier un registre W (ou un pointeur de registre W vers un emplacement mémoire) comme source des données de mémoire de programme Flash à écrire ou comme destination pour une lecture de mémoire de programme Flash.

Pour plus d'informations et de détails sur la programmation de la mémoire programme Flash, reportez-vous au manuel de référence de la famille dsPIC33/PIC24.

TABLEAU INSTRUCTIONS FONCTIONNEMENT

Les instructions du tableau fournissent la méthode de transfert de données entre l'espace mémoire du programme Flash et l'espace mémoire des données des dispositifs dsPIC33/PIC24. Cette section fournit un résumé des instructions du tableau utilisées lors de la programmation de la mémoire programme Flash. Il existe quatre instructions de table de base :

- TBLRDL : Table Lire bas

- TBLRDH : Tableau Lire Haut

- TBLWTL : Tableau Ecriture basse

- TBLWTH : Tableau Ecriture haute

L'instruction TBLRDL est utilisée pour lire à partir des bits [15:0] de l'espace mémoire du programme. L'instruction TBLWTL est utilisée pour écrire dans les bits [15:0] de l'espace mémoire du programme Flash. TBLRDL et TBLWTL peuvent accéder à la mémoire programme Flash en mode mot ou en mode octet.

Les instructions TBLRDH et TBLWTH sont utilisées pour lire ou écrire dans les bits [23:16] de l'espace mémoire du programme. TBLRDH et TBLWTH peuvent accéder à la mémoire programme Flash en mode mot ou octet. Comme la mémoire programme Flash n'a qu'une largeur de 24 bits, les instructions TBLRDH et TBLWTH peuvent adresser un octet supérieur de la mémoire programme Flash qui n'existe pas. Cet octet est appelé « octet fantôme ». Toute lecture de l'octet fantôme renverra 0x00. Une écriture dans l'octet fantôme n'a aucun effet. La mémoire programme Flash 24 bits peut être considérée comme deux espaces 16 bits côte à côte, chaque espace partageant la même plage d'adresses. Ainsi, les instructions TBLRDL et TBLWTL accèdent à l'espace mémoire programme "bas" (PM[15:0]). Les instructions TBLRDH et TBLWTH accèdent à l'espace mémoire programme "haut" (PM[31:16]). Toute lecture ou écriture dans PM[31:24] accédera à l'octet fantôme (non implémenté). Lorsque l'une des instructions de table est utilisée en mode octet, le bit le moins significatif (LSb) de l'adresse de table sera utilisé comme bit de sélection d'octet. Le LSb détermine quel octet dans l'espace de mémoire de programme haut ou bas est accédé.

La figure 2-1 illustre l'adressage de la mémoire programme Flash à l'aide des instructions du tableau. Une adresse de mémoire de programme 24 bits est formée à l'aide des bits [7: 0] du registre TBLPAG et de l'adresse effective (EA) d'un registre W spécifié dans l'instruction de table. Le compteur de programme (PC) 24 bits est illustré à la Figure 2-1 à titre de référence. Les 23 bits supérieurs de l'EA sont utilisés pour sélectionner l'emplacement de la mémoire du programme Flash.

Pour les instructions de la table en mode Octet, le LSb du registre W EA est utilisé pour sélectionner quel octet du mot mémoire programme Flash 16 bits est adressé ; '1' sélectionne les bits[15:8] et '0' sélectionne les bits[7:0]. Le LSb du registre W EA est ignoré pour une instruction de table en mode Word. En plus de l'adresse de la mémoire du programme Flash, l'instruction de table spécifie également un registre W (ou un pointeur de registre W vers un emplacement mémoire), qui est la source des données de la mémoire du programme Flash à écrire, ou la destination d'un programme Flash. mémoire lue. Pour une opération d'écriture de table en mode Byte, les bits[15:8] du registre de travail source sont ignorés.

Utilisation des instructions de lecture de table

Les lectures de table nécessitent deux étapes :

- Le pointeur d'adresse est configuré à l'aide du registre TBLPAG et de l'un des registres W.

- Le contenu de la mémoire de programme Flash à l'emplacement de l'adresse peut être lu.

- LIRE LE MODE MOT

Le code affiché dans Example 2-1 et Example 2-2 montre comment lire un mot de la mémoire programme Flash à l'aide des instructions du tableau en mode Mot.

- MODE LECTURE OCTET

Le code affiché dans Example 2-3 montre l'opérateur de post-incrémentation à la lecture de l'octet de poids faible, qui provoque l'incrémentation de un de l'adresse dans le registre de travail. Cela définit EA[0] sur un '1' pour l'accès à l'octet du milieu dans la troisième instruction d'écriture. La dernière post-incrémentation remet W0 à une adresse paire, pointant vers l'emplacement mémoire du programme Flash suivant.

- LOQUETS D'ECRITURE DE TABLE

Les instructions d'écriture de table n'écrivent pas directement dans la mémoire programme non volatile. Au lieu de cela, les instructions d'écriture de table chargent des verrous d'écriture qui stockent les données d'écriture. Les registres d'adresse NVM doivent être chargés avec la première adresse où les données verrouillées doivent être écrites. Lorsque tous les verrous d'écriture ont été chargés, l'opération de programmation de mémoire proprement dite est démarrée en exécutant une séquence spéciale d'instructions. Lors de la programmation, le matériel transfère les données des verrous d'écriture vers la mémoire Flash. Les verrous d'écriture commencent toujours à l'adresse 0xFA0000 et s'étendent jusqu'à 0xFA0002 pour la programmation par mot, ou jusqu'à 0xFA00FE pour les appareils qui ont une programmation par ligne.

Note: Le nombre de verrous d'écriture varie selon l'appareil. Reportez-vous au chapitre « Flash Program Memory » de la fiche technique spécifique de l'appareil pour connaître le nombre de verrous d'écriture disponibles.

REGISTRES DE CONTROLE

Plusieurs registres de fonctions spéciales (SFR) sont utilisés pour programmer les opérations d'effacement et d'écriture de la mémoire du programme Flash : NVMCON, NVMKEY et les registres d'adresse NVM, NVMADR et NVMADRU.

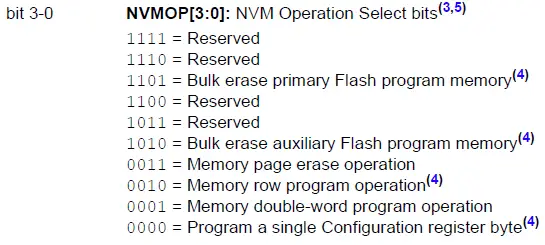

Registre NVMCON

Le registre NVMCON est le registre de contrôle principal pour les opérations Flash et de programmation/effacement. Ce registre sélectionne si une opération d'effacement ou de programmation sera effectuée et peut démarrer le programme ou le cycle d'effacement. Le registre NVMCON est affiché dans le registre 3-1. L'octet inférieur de NVMCON configure le type d'opération NVM qui sera effectuée.

Registre NVMKEY

Le registre NVMKEY (voir Registre 3-4) est un registre en écriture seule utilisé pour empêcher les écritures accidentelles de NVMCON qui peuvent corrompre la mémoire Flash. Une fois déverrouillé, les écritures sur NVMCON sont autorisées pour un cycle d'instructions dans lequel le bit WR peut être défini pour invoquer une routine d'effacement ou de programme. Compte tenu des exigences de synchronisation, la désactivation des interruptions est nécessaire.

Effectuez les étapes suivantes pour démarrer une séquence d'effacement ou de programmation :

- Désactiver les interruptions.

- Écrivez 0x55 dans NVMKEY.

- Écrivez 0xAA dans NVMKEY.

- Démarrez le cycle d'écriture de programmation en définissant le bit WR (NVMCON[15]).

- Exécutez deux instructions NOP.

- Restaurer les interruptions.

DÉSACTIVATION DES INTERRUPTIONS

La désactivation des interruptions est requise pour toutes les opérations Flash afin de garantir un résultat réussi. Si une interruption se produit pendant la séquence de déverrouillage NVMKEY, elle peut bloquer l'écriture sur le bit WR. La séquence de déverrouillage NVMKEY doit être exécutée sans interruption, comme indiqué dans la section 3.2 « Registre NVMKEY ».

Les interruptions peuvent être désactivées selon l'une des deux méthodes suivantes, en désactivant l'activation d'interruption globale (bit GIE) ou en utilisant l'instruction DISI. L'instruction DISI n'est pas recommandée car elle ne désactive que les interruptions de priorité 6 ou inférieure ; par conséquent, la méthode Global Interrupt Enable doit être utilisée.

Les écritures CPU sur GIE prennent deux cycles d'instructions avant d'affecter le flux de code. Deux instructions NOP sont nécessaires par la suite, ou peuvent être remplacées par toute autre instruction de travail utile, telle que le chargement de NVMKEY ; cela s'applique aux opérations set et clear. Des précautions doivent être prises lors de la réactivation des interruptions afin que la routine ciblée NVM n'autorise pas les interruptions lorsqu'une fonction appelée précédente les a désactivées pour d'autres raisons. Pour résoudre ce problème dans l'assemblage, un push et un pop de pile peuvent être utilisés pour conserver l'état du bit GIE. En C, une variable dans la RAM peut être utilisée pour stocker INTCON2 avant d'effacer GIE. Utilisez la séquence suivante pour désactiver les interruptions :

- Poussez INTCON2 sur la pile.

- Effacez le bit GIE.

- Deux NOP ou écritures sur NVMKEY.

- Démarrez le cycle de programmation en définissant le bit WR (NVMCON[15]).

- Restaurer l'état GIE par POP de INTCON2.

Registres d'adresses NVM

Les deux registres d'adresse NVM, NVMADRU et NVMADR, lorsqu'ils sont concaténés, forment l'EA 24 bits de la ligne ou du mot sélectionné pour les opérations de programmation. Le registre NVMADRU est utilisé pour contenir les huit bits supérieurs de l'EA, et le registre NVMADR est utilisé pour contenir les 16 bits inférieurs de l'EA. Certains appareils peuvent faire référence à ces mêmes registres comme NVMADRL et NVMADRH. Les registres d'adresse NVM doivent toujours pointer vers une limite de mot d'instruction double lors de l'exécution d'une opération de programmation de mot d'instruction double, une limite de ligne lors de l'exécution d'une opération de programmation de ligne ou une limite de page lors de l'exécution d'une opération d'effacement de page.

Registre 3-1 : NVMCON : registre de contrôle de la mémoire flash

Note

- Ce bit ne peut être réinitialisé (c'est-à-dire effacé) que lors d'une réinitialisation à la mise sous tension (POR).

- Lorsque vous quittez le mode inactif, il y a un délai de mise sous tension (TVREG) avant que la mémoire de programme Flash ne devienne opérationnelle. Reportez-vous au chapitre « Caractéristiques électriques » de la fiche technique de l'appareil spécifique pour plus d'informations.

- Toutes les autres combinaisons de NVMOP[3:0] ne sont pas implémentées.

- Cette fonctionnalité n'est pas disponible sur tous les appareils. Reportez-vous au chapitre « Flash Program Memory » de la fiche technique spécifique de l'appareil pour connaître les opérations disponibles.

- L'entrée dans un mode d'économie d'énergie après l'exécution d'une instruction PWRSAV dépend de l'achèvement de toutes les opérations NVM en attente.

- Ce bit n'est disponible que sur les périphériques qui prennent en charge la programmation de lignes en mémoire tampon RAM. Reportez-vous à la fiche technique spécifique à l'appareil pour connaître la disponibilité.

Note

- Ce bit ne peut être réinitialisé (c'est-à-dire effacé) que lors d'une réinitialisation à la mise sous tension (POR).

- Lorsque vous quittez le mode inactif, il y a un délai de mise sous tension (TVREG) avant que la mémoire de programme Flash ne devienne opérationnelle. Reportez-vous au chapitre « Caractéristiques électriques » de la fiche technique de l'appareil spécifique pour plus d'informations.

- Toutes les autres combinaisons de NVMOP[3:0] ne sont pas implémentées.

- Cette fonctionnalité n'est pas disponible sur tous les appareils. Reportez-vous au chapitre « Flash Program Memory » de la fiche technique spécifique de l'appareil pour connaître les opérations disponibles.

- L'entrée dans un mode d'économie d'énergie après l'exécution d'une instruction PWRSAV dépend de l'achèvement de toutes les opérations NVM en attente.

- Ce bit n'est disponible que sur les périphériques qui prennent en charge la programmation de lignes en mémoire tampon RAM. Reportez-vous à la fiche technique spécifique à l'appareil pour connaître la disponibilité.

Registre 3-2 : NVMADRU : registre d'adresse supérieur de la mémoire non volatile

Registre 3-3 : NVMADR : registre d'adresses de mémoire non volatile

Registre 3-4 : NVMKEY : registre de clé de mémoire non volatile

AUTO-PROGRAMMATION DU TEMPS D'EXÉCUTION (RTSP)

RTSP permet à l'application utilisateur de modifier le contenu de la mémoire du programme Flash. RTSP est réalisé à l'aide des instructions TBLRD (Table Read) et TBLWT (Table Write), du registre TBLPAG et des registres de contrôle NVM. Avec RTSP, l'application utilisateur peut effacer une seule page de mémoire Flash et programmer soit deux mots d'instruction, soit jusqu'à 128 mots d'instruction sur certains appareils.

Fonctionnement RTSP

The dsPIC33/PIC24 Flash program memory array is organized into erase pages that can contain up to 1024 instructions. The double-word programming option is available in all devices in the dsPIC33/PIC24 families. In addition, certain devices have row programming capability, which allows the programming of up to 128 instruction words at a time. Programming and erase operations always occur on an even double programming word, row or page boundaries. Refer to the “Flash Program Memory” chapter of the specific device data sheet for the availability and sizes of a programming row, and the page size for erasing. The Flash program memory implements holding buffers, called write latches, that can contain up to 128 instructions of programming data depending on the device. Prior to the actual programming operation, the write data must be loaded into the write latches. The basic sequence for RTSP is to set up the Table Pointer, TBLPAG register, and then perform a series of TBLWT instructions to load the write latches. Programming is performed by setting the control bits in the NVMCON register. The number of TBLWTL and TBLWTH instructions needed to load the write latches is equal to the number of program words to be written.

Note: Il est recommandé de sauvegarder le registre TBLPAG avant toute modification et de le restaurer après utilisation.

PRUDENCE

Sur certains appareils, les bits de configuration sont stockés dans la dernière page de l'espace mémoire utilisateur Flash du programme dans une section intitulée "Octets de configuration Flash". Avec ces appareils, effectuer une opération d'effacement de page sur la dernière page de la mémoire programme efface les octets de configuration Flash, ce qui permet la protection du code. Par conséquent, les utilisateurs ne doivent pas effectuer d'opérations d'effacement de page sur la dernière page de la mémoire programme. Ce n'est pas un problème lorsque les bits de configuration sont stockés dans l'espace mémoire de configuration dans une section intitulée « Registres de configuration des périphériques ». Reportez-vous à la carte mémoire du programme dans le chapitre « Organisation de la mémoire » de la fiche technique de l'appareil spécifique pour déterminer où se trouvent les bits de configuration.

Opérations de programmation Flash

A program or erase operation is necessary for programming or erasing the internal Flash program memory in RTSP mode. The program or erase operation is automatically timed by the device (refer to the specific device data sheet for timing information). Setting the WR bit (NVMCON[15]) starts the operation. The WR bit is automatically cleared when the operation is finished. The CPU stalls until the programming operation is finished. The CPU will not execute any instructions or respond to interrupts during this time. If any interrupts occur during the programming cycle, they will remain pending until the cycle completes. Some dsPIC33/PIC24 devices may provide auxiliary Flash program memory (refer to the “Memory Organization” chapter of the specific device data sheet for details), which allows instruction execution without CPU Stalls while user Flash program memory is being erased and/ or programmed. Conversely, auxiliary Flash program memory can be programmed without CPU Stalls, as long as code is executed from the user Flash program memory. The NVM interrupt can be used to indicate that the programming operation is complete.

Note

- Si un événement POR ou BOR se produit alors qu'une opération d'effacement ou de programmation RTSP est en cours, l'opération RTSP est immédiatement abandonnée. L'utilisateur doit exécuter à nouveau l'opération RTSP une fois que l'appareil est sorti de la réinitialisation.

- Si un événement de réinitialisation EXTR, SWR, WDTO, TRAPR, CM ou IOPUWR se produit alors qu'une opération d'effacement ou de programmation RTSP est en cours, l'appareil ne sera réinitialisé qu'une fois l'opération RTSP terminée.

ALGORITHME DE PROGRAMMATION RTSP

Cette section décrit la programmation RTSP, qui se compose de trois processus principaux.

Création d'une image RAM de la page de données à modifier

Effectuez ces deux étapes pour créer une image RAM de la page de données à modifier :

- Lisez la page de la mémoire de programme Flash et stockez-la dans la RAM de données en tant qu'« image » de données. L'image RAM doit être lue à partir d'une limite d'adresse de page.

- Modifiez l'image des données RAM si nécessaire.

Erasing Flash Program Memory

Après avoir terminé les étapes 1 et 2 ci-dessus, effectuez les quatre étapes suivantes pour effacer la page de mémoire de programme Flash :

- Définissez les bits NVMOP[3:0] (NVMCON[3:0]) pour effacer la page de mémoire de programme Flash lue à l'étape 1.

- Écrivez l'adresse de début de la page à effacer dans les registres NVMADRU et NMVADR.

- Avec les interruptions désactivées :

- a) Écrivez la séquence de touches dans le registre NVMKEY pour activer le réglage du bit WR (NVMCON[15]).

- b) Définissez le bit WR ; cela lancera le cycle d'effacement.

- c) Exécutez deux instructions NOP.

- Le bit WR est effacé lorsque le cycle d'effacement est terminé.

Programmation de la page de mémoire flash

La partie suivante du processus consiste à programmer la page de mémoire Flash. La page de mémoire flash est programmée à l'aide des données de l'image créée à l'étape 1. Les données sont transférées aux verrous d'écriture par incréments de mots d'instruction doubles ou de rangées. Tous les dispositifs ont une capacité de programmation de mot d'instruction double. (Reportez-vous au chapitre « Flash Program Memory » de la fiche technique de l'appareil spécifique pour déterminer si et quel type de programmation de ligne est disponible.) Une fois les verrous d'écriture chargés, l'opération de programmation est lancée, ce qui transfère les données de la écrire des verrous dans la mémoire Flash. Ceci est répété jusqu'à ce que toute la page ait été programmée. Répétez les trois étapes suivantes, en commençant par le premier mot d'instruction de la page Flash et en incrémentant par étapes de mots de programme doubles ou de rangées d'instructions, jusqu'à ce que la page entière ait été programmée :

- Chargez les verrous d'écriture :

- a) Définissez le registre TBLPAG pour qu'il pointe vers l'emplacement des verrous d'écriture.

- b) Chargez le nombre de bascules souhaité à l'aide de paires d'instructions TBLWTL et TBLWTH :

- Pour la programmation à double mot, deux paires d'instructions TBLWTL et TBLWTH sont nécessaires

- Pour la programmation de ligne, une paire d'instructions TBLWTL et TBLWTH est requise pour chaque élément de ligne de mot d'instruction

- Lancer l'opération de programmation :

- a) Définissez les bits NVMOP[3:0] (NVMCON[3:0]) pour programmer des mots d'instruction doubles ou une ligne d'instruction, selon le cas.

b) Écrivez la première adresse du mot d'instruction double ou de la rangée d'instructions à programmer dans les registres NVMADRU et NVMADR.

c) Avec les interruptions désactivées :

• Écrire la séquence de touches dans le registre NVMKEY pour activer le réglage du bit WR (NVMCON[15])

• Définissez le bit WR ; cela lancera le cycle d'effacement

• Exécuter deux instructions NOP

- a) Définissez les bits NVMOP[3:0] (NVMCON[3:0]) pour programmer des mots d'instruction doubles ou une ligne d'instruction, selon le cas.

- Le bit WR est effacé lorsque le cycle de programmation est terminé.

Répétez l'ensemble du processus si nécessaire pour programmer la quantité souhaitée de mémoire de programme Flash.

Note

- L'utilisateur doit se rappeler que la quantité minimale de mémoire de programme Flash pouvant être effacée à l'aide de RTSP est une seule page effacée. Par conséquent, il est important qu'une image de ces emplacements soit stockée dans la mémoire RAM à usage général avant qu'un cycle d'effacement ne soit initié.

- Une ligne ou un mot dans la mémoire programme Flash ne doit pas être programmé plus de deux fois avant d'être effacé.

- Sur les appareils avec des octets de configuration stockés dans la dernière page de Flash, effectuer une opération d'effacement de page sur la dernière page de la mémoire programme efface les octets de configuration, ce qui active la protection du code. Sur ces appareils, la dernière page de la mémoire Flash ne doit pas être effacée.

ERASING ONE PAGE OF FLASH

La séquence de code indiquée dans ExampLe 4-1 peut être utilisé pour effacer une page de la mémoire programme Flash. Le registre NVMCON est configuré pour effacer une page de la mémoire programme. Les registres NVMADR et NMVADRU sont chargés avec l'adresse de début de la page à effacer. La mémoire programme doit être effacée à une limite d'adresse de page « paire ». Voir le chapitre « Flash Program Memory » de la fiche technique spécifique de l'appareil pour déterminer la taille de la page Flash.

L'opération d'effacement est lancée en écrivant un déverrouillage spécial, ou une séquence de touches, dans le registre NVMKEY avant de définir le bit WR (NVMCON[15]). La séquence de déverrouillage doit être exécutée dans l'ordre exact, comme indiqué dans Example 4-1, sans interruption ; par conséquent, les interruptions doivent être désactivées.

Deux instructions NOP doivent être insérées dans le code après le cycle d'effacement. Sur certains appareils, les bits de configuration sont stockés dans la dernière page du programme Flash. Avec ces appareils, l'exécution d'une opération d'effacement de page sur la dernière page de la mémoire programme efface les octets de configuration Flash, permettant ainsi la protection du code. Les utilisateurs ne doivent pas effectuer d'opérations d'effacement de page sur la dernière page de la mémoire programme.

CHARGEMENT DES VERROUS D'ECRITURE

Les verrous d'écriture sont utilisés comme mécanisme de stockage entre les écritures de table de l'application utilisateur et la séquence de programmation réelle. Pendant l'opération de programmation, l'appareil transférera les données des verrous d'écriture dans la mémoire Flash. Pour les appareils prenant en charge la programmation de lignes, Example 4-3 montre la séquence d'instructions permettant de charger 128 verrous d'écriture (128 mots d'instruction). Les instructions 128 TBLWTL et 128 TBLWTH sont nécessaires pour charger les verrous d'écriture pour la programmation d'une ligne de mémoire de programme Flash. Reportez-vous au chapitre « Flash Program Memory » de la fiche technique spécifique de l'appareil pour déterminer le nombre de verrous de programmation disponibles sur votre appareil. Pour les appareils qui ne prennent pas en charge la programmation de lignes, Example 4-4 montre la séquence d'instructions permettant de charger deux verrous d'écriture (deux mots d'instruction). Deux instructions TBLWTL et deux instructions TBLWTH sont nécessaires pour charger les verrous d'écriture.

Note

- Le code pour Load_Write_Latch_Row est affiché dans Example 4-3 et le code pour Load_Write_Latch_Word est montré dans Example 4-4. Le code dans ces deux examples est mentionné dans les ex suivantsamples.

- Se référer à la fiche technique spécifique de l'appareil pour le nombre de verrous.

PROGRAMMATION RANGÉE UNIQUE EXAMPLE

Le registre NVMCON est configuré pour programmer une ligne de mémoire de programme Flash. L'opération du programme est lancée en écrivant un déverrouillage spécial, ou une séquence de touches, dans le registre NVMKEY avant de définir le bit WR (NVMCON[15]). La séquence de déverrouillage doit être exécutée sans interruption et dans l'ordre exact, comme indiqué dans Example 4-5. Par conséquent, les interruptions doivent être désactivées avant d'écrire la séquence.

Note: Tous les appareils n'ont pas la capacité de programmation de rangée. Reportez-vous au chapitre « Flash Program Memory » de la fiche technique spécifique de l'appareil pour déterminer si cette option est disponible.

Deux instructions NOP doivent être insérées dans le code après le cycle de programmation.

PROGRAMMATION DE RANG À L'AIDE DU BUFFER RAM

Certains dispositifs dsPIC33 permettent d'effectuer la programmation de ligne directement à partir d'un espace tampon dans la RAM de données, plutôt que de passer par les verrous de maintien pour transférer des données avec des instructions TBLWT. L'emplacement du tampon RAM est déterminé par le ou les registres NVMSRCADR, qui sont chargés avec l'adresse RAM de données contenant le premier mot de données de programme à écrire.

Avant d'effectuer l'opération de programmation, l'espace tampon dans la RAM doit être chargé avec la ligne de données à programmer. La RAM peut être chargée dans un format compressé (compressé) ou non compressé. Le stockage compressé utilise un mot de données pour stocker les octets les plus significatifs (MSB) de deux mots de données de programme adjacents. Le format non compressé utilise deux mots de données pour chaque mot de données de programme, l'octet supérieur de chaque autre mot étant 00h. Le format compressé utilise environ 3/4 de l'espace dans la RAM de données par rapport au format non compressé. Le format non compressé, d'autre part, imite la structure du mot de données de programme 24 bits, complet avec l'octet fantôme supérieur. Le format de données est sélectionné par le bit RPDF (NVMCON[9]). Ces deux formats sont illustrés à la Figure 4-1.

Une fois le tampon RAM chargé, les pointeurs d'adresse Flash, NVMADR et NVMADRU, sont chargés avec l'adresse de début 24 bits de la ligne Flash à écrire. Comme pour la programmation des verrous d'écriture, le processus est lancé en écrivant la séquence de déverrouillage NVM, suivie de la définition du bit WR. Une fois lancé, l'appareil charge automatiquement les bons verrous et incrémente les registres d'adresses NVM jusqu'à ce que tous les octets aient été programmés. Example 4-7 montre un example processus. Si NVMSRCADR est défini sur une valeur telle qu'une condition d'erreur de sous-utilisation des données se produit, le bit URERR (NVMCON[8]) sera défini pour indiquer la condition.

Les dispositifs qui implémentent la programmation de rangée de tampon RAM implémentent également un ou deux verrous d'écriture. Ceux-ci sont chargés à l'aide des instructions TBLWT et sont utilisés pour effectuer des opérations de programmation de mots.

PROGRAMMATION PAR MOTS

Le registre NVMCON est configuré pour programmer deux mots d'instruction de la mémoire de programme Flash. L'opération du programme est lancée en écrivant un déverrouillage spécial, ou une séquence de touches, dans le registre NVMKEY avant de définir le bit WR (NVMCON[15]). La séquence de déverrouillage doit être exécutée dans l'ordre exact, comme indiqué dans Example 4-8, sans interruption. Par conséquent, les interruptions doivent être désactivées avant d'écrire la séquence.

Deux instructions NOP doivent être insérées dans le code après le cycle de programmation.

Écriture dans les registres de configuration de périphérique

Sur certains appareils, les bits de configuration sont stockés dans l'espace mémoire de configuration dans une section intitulée « Registres de configuration des appareils ». Sur d'autres appareils, les bits de configuration sont stockés dans la dernière page de l'espace mémoire utilisateur Flash du programme dans une section appelée "Octets de configuration Flash". Avec ces appareils, effectuer une opération d'effacement de page sur la dernière page de la mémoire programme efface les octets de configuration Flash, ce qui permet la protection du code. Par conséquent, les utilisateurs ne doivent pas effectuer d'opérations d'effacement de page sur la dernière page de la mémoire programme. Reportez-vous à la carte mémoire du programme dans le chapitre « Organisation de la mémoire » de la fiche technique de l'appareil spécifique pour déterminer où se trouvent les bits de configuration.

Lorsque les bits de configuration sont stockés dans l'espace mémoire de configuration, RTSP peut être utilisé pour écrire dans les registres de configuration de l'appareil, et RTSP permet à chaque registre de configuration d'être réécrit individuellement sans effectuer au préalable un cycle d'effacement. Il faut faire preuve de prudence lors de l'écriture des registres de configuration car ils contrôlent les paramètres de fonctionnement critiques de l'appareil, tels que la source d'horloge système, l'activation PLL et WDT.

La procédure de programmation d'un registre de configuration d'équipement est similaire à la procédure de programmation de la mémoire de programme Flash, sauf que seules les instructions TBLWTL sont nécessaires. Cela est dû au fait que les huit bits supérieurs de chaque registre de configuration de périphérique ne sont pas utilisés. De plus, le bit 23 de l'adresse Table Write doit être défini pour accéder aux registres de configuration. Reportez-vous à « Device Configuration » (DS70000618) dans le « dsPIC33/PIC24 Family Reference Manual » et au chapitre « Special Features » dans la fiche technique spécifique de l'appareil pour une description complète des registres de configuration de l'appareil.

Note

- L'écriture dans les registres de configuration de l'appareil n'est pas disponible sur tous les appareils. Reportez-vous au chapitre « Caractéristiques spéciales » de la fiche technique de l'appareil spécifique pour déterminer les modes disponibles en fonction de la définition des bits NVMOP[3:0] spécifiques à l'appareil.

- Lors de l'exécution de RTSP sur les registres de configuration de l'appareil, l'appareil doit fonctionner à l'aide de l'oscillateur FRC interne (sans PLL). Si l'appareil fonctionne à partir d'une source d'horloge différente, une commutation d'horloge vers l'oscillateur FRC interne (NOSC[2:0] = 000) doit être effectuée avant d'effectuer l'opération RTSP dans les registres de configuration de l'appareil.

- Si les bits de sélection du mode d'oscillateur principal (POSCMD[1:0]) dans le registre de configuration de l'oscillateur (FOSC) sont reprogrammés à une nouvelle valeur, l'utilisateur doit s'assurer que les bits du mode de commutation d'horloge (FCKSM[1:0]) dans le registre FOSC a une valeur programmée initiale de '0', avant d'effectuer cette opération RTSP.

ALGORITHME D'ECRITURE DU REGISTRE DE CONFIGURATION

La procédure générale est la suivante :

- Écrivez la nouvelle valeur de configuration dans le verrou d'écriture de table à l'aide d'une instruction TBLWTL.

- Configurez NVMCON pour une écriture dans le registre de configuration (NVMCON = 0x4000).

- Écrivez l'adresse du registre de configuration à programmer dans les registres NVMADRU et NVMADR.

- Désactiver les interruptions, si elles sont activées.

- Écrivez la séquence de touches dans le registre NVMKEY.

- Démarrez la séquence d'écriture en définissant le bit WR (NVMCON[15]).

- Réactivez les interruptions, si nécessaire.

Example 4-10 montre la séquence de code qui peut être utilisée pour modifier un registre de configuration d'un équipement.

INSCRIPTION CARTE

Un récapitulatif des registres associés à la programmation Flash est fourni dans le Tableau 5-1.

Cette section répertorie les notes d'application liées à cette section du manuel. Ces notes d'application peuvent ne pas être écrites spécifiquement pour les familles de produits dsPIC33/PIC24, mais les concepts sont pertinents et peuvent être utilisés avec des modifications et des limitations possibles. Les notes d'application actuelles liées à la programmation Flash sont :

Note: Veuillez visiter la micropuce website (www.microchip.com) pour les notes d'application supplémentaires et le code exampfichiers pour les familles de dispositifs dsPIC33/PIC24.

HISTORIQUE DE RÉVISION

Révision A (août 2009)

Il s'agit de la version initiale publiée de ce document.

Révision B (février 2011)

Cette révision inclut les mises à jour suivantes :

- Examples:

- Ex suppriméample 5-3 et Example 5-4

- Ex mis à jourample 4-1,Example 4-5 et Example 4-10

- Toutes les références à #WR ont été mises à jour à #15 dans Example 4-1,Example 4-5 et Example 4-8

- Mise à jour des éléments suivants dans Example 4-3 :

- Mise à jour du titre "Programmation de mots" en "Chargement des verrous d'écriture pour la programmation de lignes"

- Toute référence à #ram_image a été mise à jour vers #0xFA

- Ex ajoutéample 4-4

- Mise à jour du titre dans Example 4-8

- Remarques :

- Ajout de deux notes dans la section 4.2 "Opérations de programmation Flash"

- Mise à jour de la note de la section 4.5.2 « Chargement des verrous d'écriture »

- Ajout de trois notes dans la section 4.6 « Écriture dans les registres de configuration des périphériques »

- Remarque 1 ajoutée dans le tableau 5-1

- Registres:

- Mise à jour des valeurs de bit pour NVMOP[3:0] : NVM Operation Select bits dans le registre de contrôle de la mémoire flash (NVMCON) (voir registre 3-1)

- Rubriques :

- Suppression des sections 5.2.1.4 "Write Word Mode" et 5.2.1.5 "Write Byte Mode"

- Mise à jour de la section 3.0 « Registres de contrôle »

- Mise à jour des éléments suivants dans la section 4.5.5 « Programmation de mots » :

- Modification du titre de la section "Programmation d'un mot de la mémoire flash" en "Programmation de mots"

- Mise à jour du premier paragraphe

- Changement des termes « un mot » en « une paire de mots » dans le deuxième paragraphe

- Ajout d'une nouvelle étape 1 à la section 4.6.1 « Algorithme d'écriture du registre de configuration »

- Tableaux:

- Tableau 5-1 mis à jour

- Quelques références à la mémoire programme ont été mises à jour vers la mémoire programme Flash

- D'autres mises à jour mineures telles que des mises à jour de langue et de formatage ont été incorporées dans tout le document

Révision C (juin 2011)

Cette révision inclut les mises à jour suivantes :

- Examples:

- Ex mis à jourample 4-1

- Ex mis à jourample 4-8

- Remarques :

- Ajout d'une note dans la section 4.1 "Fonctionnement RTSP"

- Ajout de la note 3 dans la section 4.2 « Opérations de programmation Flash »

- Ajout de la note 3 dans la section 4.2.1 « Algorithme de programmation RTSP »

- Added a note in Section 4.5.1 “Erasing One Page of Flash”

- Ajout de la note 2 dans la section 4.5.2 "Chargement des verrous d'écriture"

- Registres:

- Mise à jour de la description des bits pour les bits 15-0 dans le registre d'adresse de mémoire non volatile (voir registre 3-3)

- Rubriques :

- Mise à jour de la section 4.1 "Fonctionnement RTSP"

- Mise à jour de la section 4.5.5 "Programmation de mots"

- D'autres mises à jour mineures telles que des mises à jour de langue et de formatage ont été incorporées dans tout le document

Révision D (décembre 2011)

Cette révision inclut les mises à jour suivantes :

- Mise à jour de la section 2.1.3 « Verrous d'écriture de table »

- Mise à jour de la section 3.2 « Registre NVMKEY »

- Mise à jour des notes dans NVMCON : Registre de contrôle de la mémoire flash (voir Registre 3-1)

- Des mises à jour étendues ont été effectuées dans la section 4.0 "Auto-programmation d'exécution (RTSP)"

- D'autres mises à jour mineures telles que des mises à jour de langue et de formatage ont été incorporées dans tout le document

Révision E (octobre 2018)

Cette révision inclut les mises à jour suivantes :

- Ex ajoutéample 2-2,Example 4-2,Example 4-6 et Example 4-9

- Ajout de la section 4.5.4 "Programmation de lignes à l'aide du tampon RAM"

- Mise à jour de la section 1.0 "Introduction", de la section 3.3 "Registres d'adresses NVM", de la section 4.0 "Run-Time Self-Programming (RTSP)" et de la section 4.5.3 "Single Row Programming Examples"

- Mise à jour du registre 3-1

- Ex mis à jourample 4-7

- Tableau 5-1 mis à jour

Révision F (novembre 2021)

Ajout de la section 3.2.1 "Désactivation des interruptions".

Ex mis à jourample 3-1,Example 4-1,Example 4-2,Example 4-5,Example 4-6,Example 4-7,Example 4-8,Example 4-9 et Example 4-10.

Updated Section 3.2 “NVMKEY Register”, Section 4.5.1 “Erasing One Page of Flash”, Section 4.5.3 “Single Row Programming Example » et Section 4.6.1 « Algorithme d'écriture du registre de configuration ».

Notez les détails suivants concernant la fonction de protection du code sur les produits Microchip :

- Les produits Microchip répondent aux spécifications contenues dans leur fiche technique Microchip particulière.

- Microchip estime que sa gamme de produits est sécurisée lorsqu'elle est utilisée de la manière prévue, dans le cadre des spécifications de fonctionnement et dans des conditions normales.

- Microchip valorise et protège agressivement ses droits de propriété intellectuelle. Les tentatives de violation des fonctions de protection du code du produit Microchip sont strictement interdites et peuvent enfreindre le Digital Millennium Copyright Act.

- Ni Microchip ni aucun autre fabricant de semi-conducteurs ne peut garantir la sécurité de son code. La protection du code ne signifie pas que nous garantissons que le produit est « incassable ». La protection du code évolue constamment. Microchip s'engage à améliorer en permanence les fonctions de protection du code de ses produits

Cette publication et les informations qu'elle contient ne peuvent être utilisées qu'avec les produits Microchip, y compris pour concevoir, tester et intégrer les produits Microchip à votre application. L'utilisation de ces informations de toute autre manière viole ces conditions. Les informations concernant les applications de l'appareil sont fournies uniquement pour votre commodité et peuvent être remplacées par des mises à jour. Il est de votre responsabilité de vous assurer que votre application répond à vos spécifications. Contactez votre bureau de vente Microchip local pour une assistance supplémentaire ou obtenez une assistance supplémentaire sur https://www.microchip.com/en-us/support/design-help/client-supportservices.

CES INFORMATIONS SONT FOURNIES PAR MICROCHIP « EN L'ÉTAT ». MICROCHIP NE FAIT AUCUNE DÉCLARATION OU GARANTIE D'AUCUNE SORTE, QU'ELLE SOIT EXPLICITE OU IMPLICITE, ÉCRITE OU ORALE, LÉGALE OU AUTRE, RELATIVE AUX INFORMATIONS, Y COMPRIS, MAIS SANS S'Y LIMITER, TOUTE GARANTIE IMPLICITE D'ABSENCE DE CONTREFAÇON, DE QUALITÉ MARCHANDE ET D'ADÉQUATION À UN USAGE PARTICULIER, OU LES GARANTIES RELATIVES À SON ÉTAT, SA QUALITÉ OU SES PERFORMANCES. EN AUCUN CAS, MICROCHIP NE SERA RESPONSABLE DES PERTES, DOMMAGES, COÛTS OU DÉPENSES INDIRECTS, SPÉCIAUX, PUNITIFS, ACCESSOIRES OU CONSÉCUTIFS DE QUELQUE NATURE QUE CE SOIT LIÉS À L'INFORMATION OU À SON UTILISATION, QUELLE QU'EN SOIT LA CAUSE, MÊME SI MICROCHIP A ÉTÉ INFORMÉ DE LA LA POSSIBILITE OU LES DOMMAGES SONT PREVISIBLES. DANS TOUTE LA MESURE AUTORISÉE PAR LA LOI, LA RESPONSABILITÉ TOTALE DE MICROCHIP SUR TOUTES LES RÉCLAMATIONS RELATIVES AUX INFORMATIONS OU À SON UTILISATION NE DÉPASSERA PAS LE MONTANT DES FRAIS, LE CAS ÉCHÉANT, QUE VOUS AVEZ PAYÉS DIRECTEMENT À MICROCHIP POUR LES INFORMATIONS.

L'utilisation des dispositifs Microchip dans des applications de maintien des fonctions vitales et/ou de sécurité est entièrement aux risques et périls de l'acheteur, qui s'engage à défendre, indemniser et dégager Microchip de toute responsabilité en cas de dommages, réclamations, poursuites ou dépenses résultant d'une telle utilisation. Aucune licence n'est transmise, implicitement ou autrement, en vertu des droits de propriété intellectuelle de Microchip, sauf indication contraire.

Pour plus d'informations sur les systèmes de gestion de la qualité de Microchip, veuillez visiter www.microchip.com/qualité.

Marques déposées

Le nom et le logo Microchip, le logo Microchip, Adaptec, AnyRate, AVR, logo AVR, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, logo Microsemi, MOST, logo MOST, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, logo PIC32, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, logo SST, SuperFlash , Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron et XMEGA sont des marques déposées de Microchip Technology Incorporated aux États-Unis et dans d'autres pays. AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, logo ProASIC Plus, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath et ZL sont des marques déposées de Microchip Technology Incorporated aux États-Unis

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM , ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, Programmation série en circuit, ICSP, INICnet, Mise en parallèle intelligente, Connectivité inter-puces, JitterBlocker, Bouton sur l'affichage, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, logo certifié MPLAB, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, génération de code omniscient, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE , Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect et ZENA sont des marques commerciales de Microchip Technology Incorporated aux États-Unis et dans d'autres pays.

SQTP est une marque de service de Microchip Technology Incorporated aux États-Unis

Le logo Adaptec, Frequency on Demand, Silicon Storage Technology, Symmcom et Trusted Time sont des marques déposées de Microchip Technology Inc. dans d'autres pays.

GestIC est une marque déposée de Microchip Technology Germany II GmbH & Co. KG, une filiale de Microchip Technology Inc., dans d'autres pays.

Toutes les autres marques commerciales mentionnées ici sont la propriété de leurs sociétés respectives.

© 2009-2021, Microchip Technology Incorporated et ses filiales.

Tous droits réservés.

ISBN: 978-1-5224-9314-3

Ventes et service dans le monde entier

AMÉRIQUES

- Siège social

2355, boulevard Chandler Ouest.

Chandler, Arizona 85224-6199

Tél.: 480-792-7200

Fax: 480-792-7277

Support technique : http://www.microchip.com/

soutien Web Adresse: www.microchip.com - Atlanta

Duluth, Géorgie

Tél.: 678-957-9614

Fax: 678-957-1455 - Austin, Texas

Tél.: 512-257-3370 - Boston

Westborough, Massachusetts

Tél.: 774-760-0087

Fax: 774-760-0088 - Chicago

Itasca, Illinois

Tél.: 630-285-0071

Fax: 630-285-0075 - Dallas

Addison, TX

Tél.: 972-818-7423

Fax: 972-818-2924 - Détroit

Novi, Michigan

Tél.: 248-848-4000 - Houston, Texas

Tél.: 281-894-5983 - Indianapolis

Noblesville, Indiana

Tél.: 317-773-8323

Fax: 317-773-5453

Tél.: 317-536-2380 - Los Angeles

Mission Viejo, Californie

Tél.: 949-462-9523

Fax: 949-462-9608

Tél.: 951-273-7800 - Raleigh, Caroline du Nord

Tél.: 919-844-7510 - New York, État de New York

Tél.: 631-435-6000 - San José, Californie

Tél.: 408-735-9110

Tél.: 408-436-4270 - Canada – Toronto

Tél.: 905-695-1980

Fax: 905-695-2078

ASIE/PACIFIQUE

- Australie – Sydney

Tél.: 61-2-9868-6733 - Chine – Pékin

Tél.: 86-10-8569-7000 - Chine – Chengdu

Tél.: 86-28-8665-5511 - Chine – Chongqing

Tél.: 86-23-8980-9588 - Chine – Dongguan

Tél.: 86-769-8702-9880 - Chine – Guangzhou

Tél.: 86-20-8755-8029 - Chine – Hangzhou

Tél.: 86-571-8792-8115 - Chine – RAS de Hong Kong

Tél.: 852-2943-5100 - Chine – Nankin

Tél.: 86-25-8473-2460 - Chine – Qingdao

Tél.: 86-532-8502-7355 - Chine – Shanghai

Tél.: 86-21-3326-8000 - Chine – Shenyang

Tél.: 86-24-2334-2829 - Chine – Shenzhen

Tél.: 86-755-8864-2200 - Chine – Suzhou

Tél.: 86-186-6233-1526 - Chine – Wuhan

Tél.: 86-27-5980-5300 - Chine – Xian

Tél.: 86-29-8833-7252 - Chine – Xiamen

Tél.: 86-592-2388138 - Chine – Zhuhai

Tél.: 86-756-3210040 - Inde – Bangalore

Tél.: 91-80-3090-4444 - Inde – New Delhi

Tél.: 91-11-4160-8631 - Inde – Pune

Tél.: 91-20-4121-0141 - Japon – Osaka

Tél.: 81-6-6152-7160 - Japon – Tokyo

Tél.: 81-3-6880-3770 - Corée – Daegu

Tél.: 82-53-744-4301 - Corée – Séoul

Tél.: 82-2-554-7200 - Malaisie – Kuala Lumpur

Tél.: 60-3-7651-7906 - Malaisie – Penang

Tél.: 60-4-227-8870 - Philippines – Manille

Tél.: 63-2-634-9065 - Singapour

Tél.: 65-6334-8870 - Taïwan – Hsin Chu

Tél.: 886-3-577-8366 - Taïwan – Kaohsiung

Tél.: 886-7-213-7830 - Taïwan – Taipei

Tél.: 886-2-2508-8600 - Thaïlande – Bangkok

Tél.: 66-2-694-1351 - Vietnam–Ho Chi Minh

Tél.: 84-28-5448-2100

EUROPE

- Autriche – Wels

Tél.: 43-7242-2244-39

Fax: 43-7242-2244-393 - Danemark – Copenhague

Tél.: 45-4485-5910

Fax: 45-4485-2829 - Finlande – Espoo

Tél. : 358-9-4520-820 - France – Paris

Tél.: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 - Allemagne – Garching

Tél.: 49-8931-9700 - Allemagne – Haan

Tél.: 49-2129-3766400 - Allemagne – Heilbronn

Tél.: 49-7131-72400 - Allemagne – Karlsruhe

Tél.: 49-721-625370 - Allemagne – Munich

Tél.: 49-89-627-144-0

Fax: 49-89-627-144-44 - Allemagne – Rosenheim

Tél.: 49-8031-354-560 - Italie – Milan

Tél.: 39-0331-742611

Fax: 39-0331-466781 - Italie – Padoue

Tél.: 39-049-7625286 - Pays-Bas – Drunen

Tél.: 31-416-690399

Fax: 31-416-690340 - Norvège – Trondheim

Tél.: 47-7288-4388 - Pologne – Varsovie

Tél.: 48-22-3325737 - Roumanie – Bucarest

Tél.: 40-21-407-87-50 - Espagne – Madrid

Tél.: 34-91-708-08-90

Fax: 34-91-708-08-91 - Suède – Göteborg

Tél.: 46-31-704-60-40 - Suède – Stockholm

Tél.: 46-8-5090-4654 - Royaume-Uni – Wokingham

Tél.: 44-118-921-5800

Fax: 44-118-921-5820

Note:

Cette section du manuel de référence de la famille est destinée à servir de complément aux fiches techniques des appareils. Selon la variante de l'appareil, cette section du manuel peut ne pas s'appliquer à tous les appareils dsPIC33/PIC24. Veuillez consulter la note au début du chapitre « Flash Program Memory » dans la fiche technique actuelle de l'appareil pour vérifier si ce document prend en charge l'appareil que vous utilisez.

Les fiches techniques des appareils et les sections du manuel de référence de la famille sont disponibles en téléchargement sur Microchip Worldwide Website à: http://www.microchip.com.

Documents / Ressources

|

Programmation Flash MICROCHIP PIC24 [pdf] Guide de l'utilisateur Programmation Flash PIC24, PIC24, Programmation Flash, Programmation |

|

Programmation Flash MICROCHIP PIC24 [pdf] Guide de l'utilisateur Programmation Flash PIC24, PIC24, Programmation Flash |